一提到先进封装必须提到RDL(重布线层),而RDL在大部分的场景下的目的都是Fan Out (扇出),以实现更轻薄、更多的IO接口、更好的电性能。在芯片设计和制造时,IO Pad一般分布在芯片的边沿或者四周。IO pad是指芯片管脚处理点位,即负责将芯片管脚的信号经过处理送给芯片内部,又会将芯片内部输出的信号经过处理送到芯片管脚。

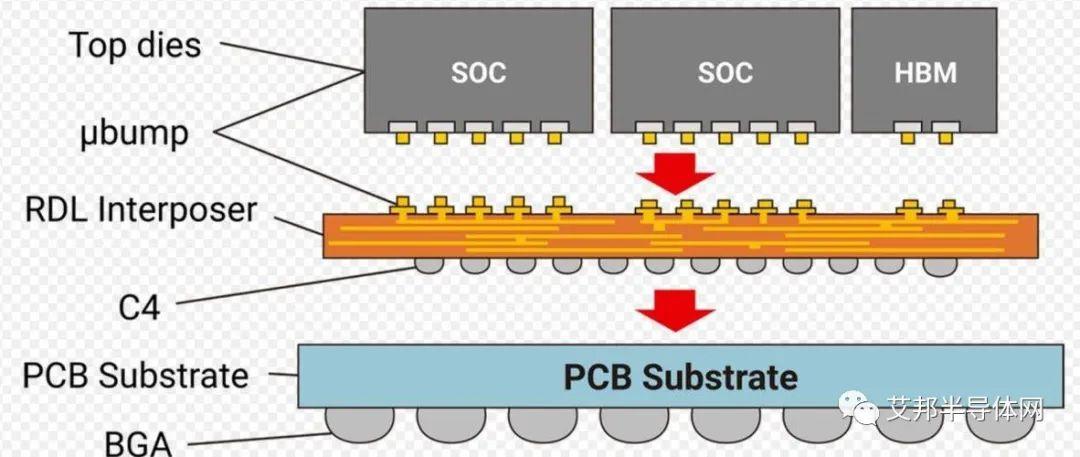

而RDL工艺是指在晶圆表面沉积金属层和相应的介质层,并形成金属布线,对IO端口进行重新布局,将其布局到新的且占位更为宽松的区域,并形成面阵列排布。RDL的另一大好处,为多芯粒横向堆叠提供了便利条件。如图1所示,多个功能不同的芯粒与PCB板之间的连接通过RDL层来实现。

图1. 台积电官网(CoWos-R)示意图

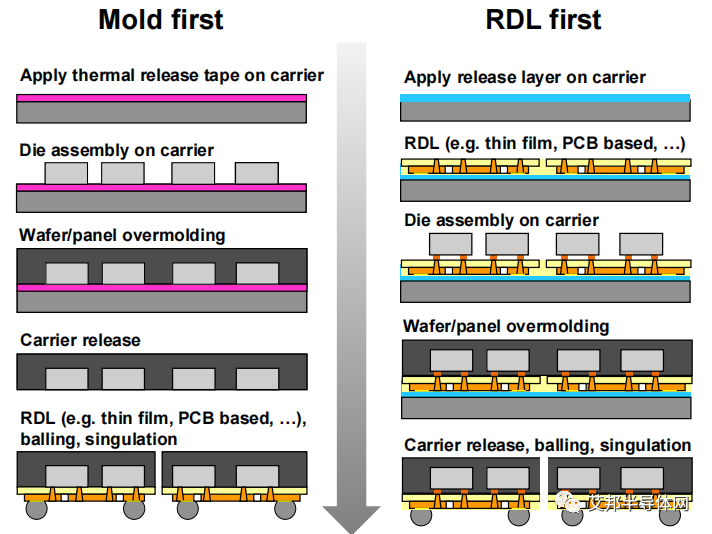

在整个Fan Out扇出工艺分为两大类型RDL First和Die First/ Mold First。而整个扇出工艺中,难点主要集中在翘曲变形、芯片贴装偏移、塑封质量等多个环节。今天我们就找几个典型的问题进行大致讲述。如果您有兴趣深入了解,欢迎加入艾邦半导体群进行讨论。

Mold First 和RDL First两个工艺路线细节如图2所示。Mold First和RDL First工艺细节在艾邦半导体公众号中已经有详细介绍,此处不再细谈。

图2. Mold First或DIE First与 RDL First或 DIE Last工艺差异

先谈谈Mold First工艺中芯粒贴装偏移问题,我们都知道精度再高的DIE Pick and Place 设备都不可能没有偏移量。而Mold First工艺中在载板上先贴或涂 release film,第二步贴adhesive tape,第三步便是贴芯粒在载板上,然后塑封并制备与芯粒IO Pad连接的RDL层。芯粒贴装(pick and place)和塑封(Molding) 在RDL制备之前,因此芯粒位置偏移主要由四方面原因导致:

一,塑封后由于塑封料固化后收缩导致芯粒位置发生变化;

二,芯粒贴装位置精度不够高;

三,塑封时由于CTEmismatch产生翘曲;

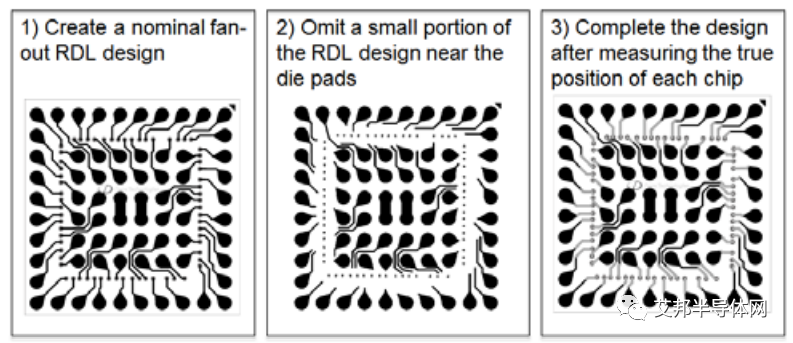

四,Adhesive tape粘力不够强,外力改变了芯粒的设定位置。一旦芯粒位置发生偏移都会给后续RDL的制备增加工艺难度,并导致良率问题。那如何解决这一问题呢?业界常用的方法有两种,一种是根据经验或模型在贴芯粒的时候进行预先补偿,提前预判塑封后由于收缩或翘曲等导致的变形。另外一种便是在制备RDL层前,对不同的芯粒IO Pad或Bump进行测量,提前将测量出来的值输入到RDL制备设备中进行提前补偿,避免错位引起的失效。如图3所示,首先创建一个标准的RDL图形,然后省略掉一部分与DIE Pad接近的RDL,最后根据测量好每个芯粒实际位置后进行重新定位以便于RDL的制备。

图3. 创建自适应模式扇出RDL层的过程

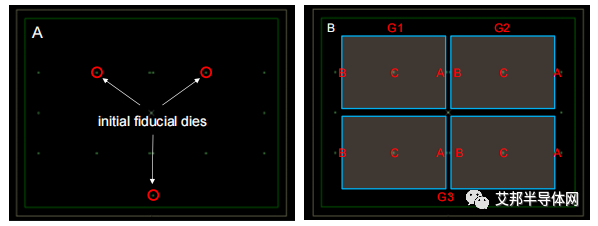

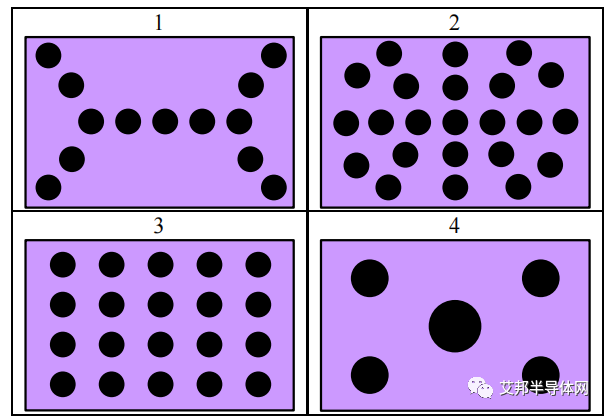

接着我们再聊聊DIE Pick and Place精度问题的解决方案,我们都知道任何贴装都需要通过Fiducial进行定位,而Mold First/DIE First工艺都需要将成百上千的芯粒先贴到基板上。因此,如何实现准确的定位就是整个工艺中的难点之一。如图4所示,在面板级封装界,通常采用的办法是将整个面板分为多个区域,例如将一个大的区域划分为四个小的部分,分别重新定位从而避免较大的累积误差。当然,这样做也会由于定位点的增加而损失一些UPH。

图4. 图A先贴3颗DIE作为Fiducial DIE或称定位DIE,然后将整个面板贴完,而图B则是将一个大的面板分为四份,每小份都分别贴定位DIE,这样就可以减少累计误差,从而提高贴装精度

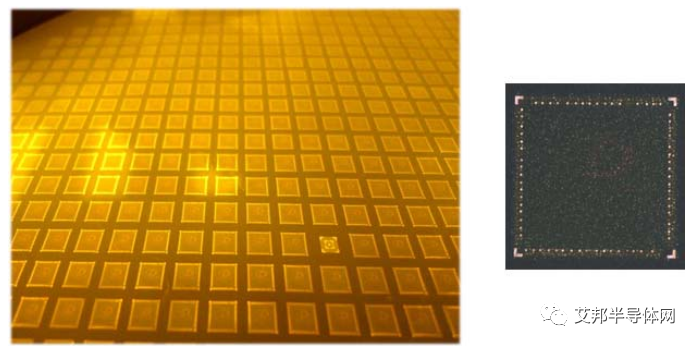

我们再仔细看一下RDL层制备前芯粒的IO Pad以及DIE 贴在面板级载板上的实物图,如图5所示。我们可以看到IO Pad分布在DIE周边一圈,而最后制备好RDL后,经过RDL扇出后均匀分布在整个DIE的平面上。

图5. DIE First 在贴装芯片都面板级载板上的实物图,右图为芯粒在晶圆厂制备好后的IO Pad分布

另外一个工艺难点便是Mold过程中整个基板的平整度以及溢料等问题的解决方案。图6可以看出,溢料的产生很容易为后续RDL的制备带来困难,主要是由于溢料会直接导致断路。业界针对该问题标准的解决方案如图7所示,在塑封前生成一定高度的铜柱,最终使得塑封料与RDL层隔开一定的距离,避免了上述由于溢料等导致的断路。也相当于通过物理隔离的办法增加了工艺的稳定性并提高了后续的良率。

图6. 芯粒(DIE)在载板上塑封后溢料的产生

图7. 通过生长一定高度Cu Pillar(铜柱),使得塑封料与RDL层隔开一定的距离

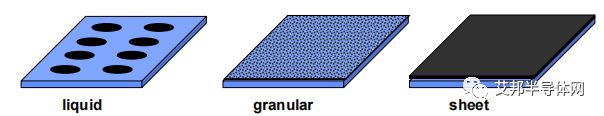

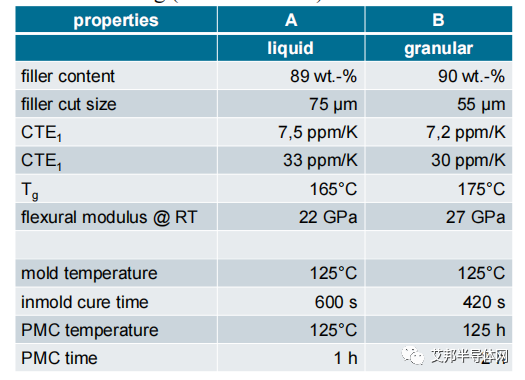

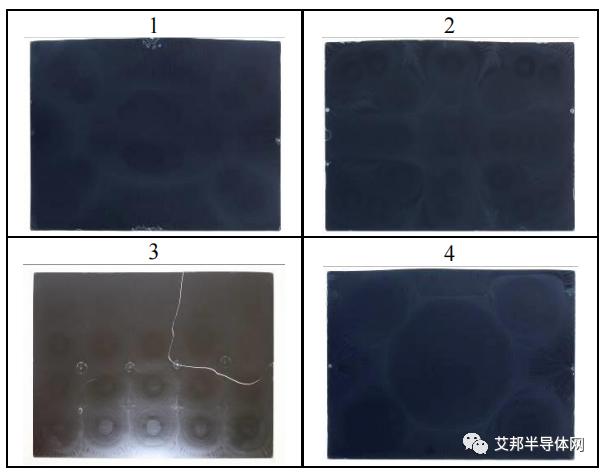

最后,我们再谈谈塑封料的选择。在先进封装塑封环节,塑封料的选型必不可少。塑封料一般分为三种:Liquid 液体,Granular:颗粒状和Sheet:片。选择不同塑封料的标准是材料应具有低化学收缩、低固化温度和相匹配的热机械性能,以满足塑封后载板的低翘曲变形和成型后的DIE位置偏移。而塑封料的流动特性应允许大空腔的均匀填充。针对液体式塑封料,液滴位置的选取也是一个非常有技巧的环节。如图10所示,不同液滴位置最终塑封后的塑封形貌。

图8. 塑封料种类:Liquid 液体,Granular:颗粒状,Sheet:片

图9. 不同塑封料类型参数对比表

图11. 全球面板级封装厂商 来自MAZN

参考文献:

Large Area Compression Molding for Fan-out Panel Level Packing T. Braun (1 ), S. Raatz (1 ), S. Voges (2 ), R. Kahle (2 ), V. Bader (1 ), J. Bauer (1 ), K.-F. Becker (1 ), T. Thomas (2 ), R. Aschenbrenner (1 ), K.-D. Lang (2 )

IMPLEMENTATION OF A FULLY MOLDED FAN-OUT PACKAGING TECHNOLOGY B. Rogers, C. Scanlan, and T. Olson